# CONSERVATOIRE NATIONAL DES ARTS ET METIERS

## **ELECTRONIQUE ANALOGIQUE** (code ELE 004)

**Seconde session**

Samedi 31 mars 2007 9h – 12h

## sans documents

<u>Tout résultat donné sans unités sera considéré comme faux</u> <u>Tout schéma électrique sans orientation des générateurs, des courants et des tensions</u> sera considéré comme faux.

Les exercices peuvent être traités dans un ordre quelconque.

#### **EXERCICE 1 dopage et JFET (5 points)**

On rappelle: Concentration intrinsèque du silicium :  $10^{10}$  cm<sup>-3</sup>.

Concentration du silicium: 5 10<sup>22</sup> cm<sup>-3</sup>

Charge de l'électron: 1,6 10<sup>-19</sup> C; mobilité des électrons: 1500cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>; mobilité des trous: 600 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>.

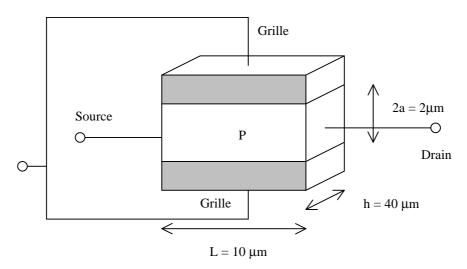

On considère le canal de type P suivant d'un transistor JFET réalisé à partir de silicium : Les grilles sont reliées entre elles.

1.

- a. Dans quelle(s) colonne(s) de la classification périodique doivent être choisis les atomes dopants pour réaliser le canal ? pour réaliser la grille ?

- b. Comment doit-on choisir la concentration des impuretés des grilles vis à vis de la concentration des impuretés du canal ?

- 2. Le canal est dopé uniformément avec une concentration d'impuretés de  $10^{17} \ \mathrm{cm}^{-3}$ .

- a . Donner la concentration en électrons libres  $n_0$  et en trous  $p_0$  du canal.

- b. Donner l'expression de la conductivité électrique et la calculer pour le canal.

- c. Calculer la résistance du canal supposé entièrement ouvert.

- 3. Pour faire fonctionner le JFET quel doit être le signe de la tension V<sub>GS</sub>? Pourquoi?

## **EXERCICE 2 : Régulation de tension. (7 pts)**

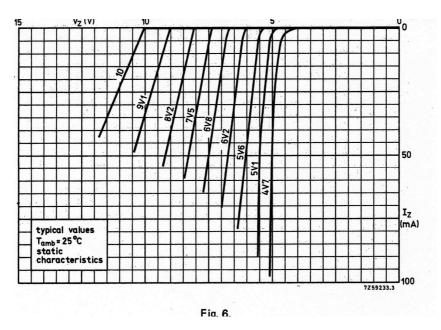

On se propose de réaliser une alimentation stabilisée avec une diode Zener 6V2. La caractéristique de la diode choisie est donnée sur le graphe du constructeur suivant.

- 1. On désire que le point de repos de la diode 6V2 soit choisi au milieu de la plage de régulation. Quelle est la valeur de cette plage et quel est le point de polarisation ?

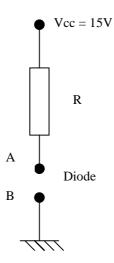

- 2. On utilise le montage de polarisation suivant de la diode.

- a) Dessiner le sens de branchement de la diode de régulation de tension sur ce schéma.

- b) Déterminer la valeur adéquate de la résistance R qui permet à cette diode d'être polarisée au point choisi dans la question 2

- c) Quelle est la résistance dynamique de cette diode au point de polarisation ?

- 3. La variation relative de la tension d'alimentation Vcc est de  $\pm$  5%. Quelle est alors la variation de la tension aux bornes de la diode ?

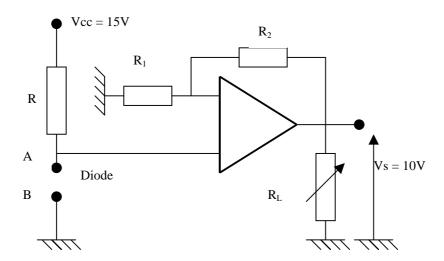

4. On réalise maintenant le régulateur suivant construit à partir d'un amplificateur opérationnel idéal :

- a) Le dessinateur a oublié de préciser la position des entrées inverseuse et non inverseuse +. Pourriez vous indiquer ces entrées sur l'amplificateur opérationnel ?

- b) On veut une tension régulée aux bornes de la charge variable  $R_L$  de 10V. Préciser la valeur de  $R_2$  si  $R_1 = 100 \ k\Omega$ .

- c) Quel est selon vous l'avantage de ce montage par rapport à un montage sans amplificateur opérationnel en ce qui concerne la résistance de charge ?

## **EXERCICE 3 Amplification (10 pts)**

Les parties I, II, sont indépendantes

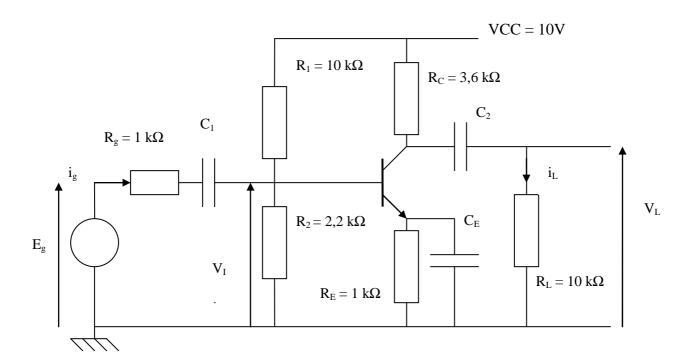

# On considère le montage suivant utilisant un transistor bipolaire npn et une alimentation VCC = +10V

Le gain statique en courant  $\beta$  nominal (typique) est de 100. La tension (VBE)<sub>on</sub> est de 0,65V.

#### I) Etude générale et polarisation

- 1) Quel est le type de montage élémentaire utilisé (E.C. B.C. C.C.)? justifier votre choix.

- 2) Quelles sont les propriétés essentielles de ce type de montage?

- 3) Dessiner le schéma valable pour la polarisation.

- 4) Donner l'expression de la droite de charge statique et tracer cette droite.

- 5) Déterminer le point de fonctionnement statique du transistor  $I_{CR}$  et  $V_{CER}$ . (R pour Repos). Ce point de fonctionnement vous semble-t-il correctement choisi ? Justifier votre réponse.

#### II) Etude en régime dynamique

Pour cette étude on supposera que les condensateurs présentent une impédance nulle à la fréquence de travail.

Les caractéristiques dynamiques du transistor sont les suivantes :

$$h_{11}=2\ k\Omega; \quad h_{12}=h_{22}=0; \ h_{21}=100.$$

- 1) Dessiner le schéma équivalent du montage valable pour les petits signaux.

- 2) Tracer sur le même graphe que celui de la question I-4 la droite de charge dynamique.

- 3) Donner les expressions littérales puis numériques du gain en tension  $A_v = V_L/V_I$ ; de l'impédance d'entrée du montage Ze et du gain composite en tension  $A_{vc} = V_L/e_{rc}$ .

- 4) Déterminer le gain en courant  $A_i = i_L/i_g$ .

- 5) Déterminer l'expression et la valeur de l'impédance de sortie de ce montage. Conclusion ou remarques sur les valeurs des gains et des impédances obtenues.

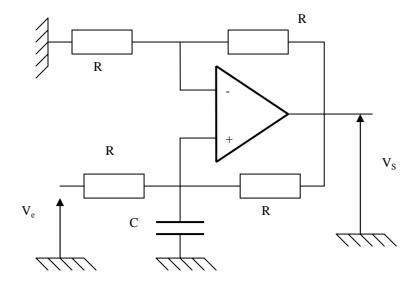

# **EXERCICE 4: Intégrateur (8 points)**

Soit le circuit suivant est réalisé au moyen d'un amplificateur opérationnel, de 4 résistances identiques R et d'un condensateur C. L'amplificateur opérationnel est supposé idéal. Il est polarisé par une alimentation double symétrique  $+V_{CC}=12V$ ;  $-V_{CC}=-12V$

- 1. On travaille dans le domaine temporel. Etablir la relation entre  $V_S(t)$  et  $V_e(t)$ . Montrer qu'il s'agit d'un circuit intégrateur et que  $V_s(t) = a \int v_e(t) dt$ . Quelle est l'expression de a en fonction de R et de C ?

- 2. Dessiner le schéma de l'intégrateur étudié en cours. Quelle est la différence entre cet intégrateur et celui de la figure ci-dessus (en dehors du nombre d'éléments) ?

- 3. Représenter la tension de sortie  $V_s(t)$  lorsque  $V_e(t)$  est un échelon de tension de 2V.  $(V_e(t)=0V \text{ pour } t<0 \text{ et } V_e(t)=2V \text{ pour } t\geq0)$ . R=  $10 \text{ k}\Omega$ ; C= 100 nF.

- 4. On se place maintenant en régime sinusoïdal permanent. Quelle est la fonction de transfert de ce circuit. Préciser le module et l'argument de cette fonction de transfert. Tracer l'allure du diagramme asymptotique de Bode du module et de la phase de ce circuit.

- 5. Les signaux d'entrée sont supposés sinusoïdaux dans la bande de fréquence [1 Hz-10~kHz]. Quelle est l'amplitude maximale de la sinusoïde d'entrée afin que les signaux soient correctement intégrés ?

- 6. Si l'amplificateur opérationnel n'est plus idéal, et possède un gain en boucle ouverte de 100 dB aux fréquences très basses et admet une fréquence de transition de 1MHz, le résultat de la question 5 sera-t-il modifié ?